# AC 2008-2186: CURRICULAR ENHANCEMENT TO SUPPORT PROJECT-BASED LEARNING IN COMPUTER AND ELECTRICAL ENGINEERING

# Albert Liddicoat, California Polytechnic State University

Albert A. Liddicoat received his M.S. and Ph.D. degrees in Electrical Engineering and his M.S. degree in Engineering Management from Stanford University in 1996, 2002 and 1999, respectively. Dr. Liddicoat worked for IBM's Storage Technology Division from 1990 until 2002 where he held many positions in disk drive development including: servo system test and integration, ASIC development, system electronics and architecture, program management, and business line management. Currently, he is the Forbes Associate Professor and the Director of the Computer Engineering Program at Cal Poly State University in San Luis Obispo. His research interests include computer architecture, computer arithmetic, networks, and re-configurable computing.

### Jianbiao Pan, California Polytechnic State University

Dr. Jianbiao (John) Pan is an assistant professor in the Department of Industrial and Manufacturing Engineering at Cal Poly, San Luis Obispo, CA. After completing a PhD at Lehigh University in Industrial Engineering in 2000, he joined the optoelectronics center at Lucent Technologies/Agere Systems as a member of technical staff. He received a M.E degree in Manufacturing Engineering from Tsinghua University, Beijing, China, and a B.E. degree in Mechatronics from Xidian University, Xian, China. Dr. Pan's research interests include electronics packaging, optoelectronics packaging, surface mount assembly, hybrid microelectronics, design and analysis of experiment, and computer aided manufacturing. He has been a Society of Manufacturing Engineers (SME) advisor on Electronics Manufacturing, and served on the National Technical Committee for the International Microelectronics and Packaging Society (IMAPS), and as Chair of SME Electronics Manufacturing Engineering Certification Committee. He is a senior member of IEEE, IMAPS, and SME, and a member of Sigma Xi and ASEE. Dr. Pan is a recipient of the 2004 M. Eugene Merchant Outstanding Young Manufacturing Engineer Award from the Society of Manufacturing Engineers (SME). He is a Highly Commended Winner of the Emerald Literati Network Awards for Excellence 2007. He is also an invitee of the National Academy of Engineering (NAE) Frontiers in Engineering Symposium in 2007.

#### James Harris, California Polytechnic State University

James G. Harris received his BS and MS in EE from UCB and the PhD in EE from Syracuse University. He was an Assistant Professor at Howard University, and an Associate Professor at the University of the District of Columbia, both in Washington, D.C. He is a Professor with the Department of Electrical Engineering, and the Computer Engineering Program at Cal Poly in San Luis Obispo, CA. He served as the Department Head of the EE Department from 1982-89 and the Director of the Computer Engineering Program from 1993-97, and starting in January 2008, he is serving as Director of the Computer Engineering Program. From 1990-92, he was a Program Director in the Division of Undergraduate Education at the National Science Foundation in Washington, D.C. He worked for TRW in Redondo Beach, CA for 11 years, primarily on signal processing projects. He is a member of IEEE, ASEE, ACM, AAAS, and SHOT.

Lynne Slivovsky, California Polytechnic State University

# Curricular Enhancement to Support Project-Based Learning in Computer and Electrical Engineering

#### Abstract

Undergraduate computer and electrical engineering programs often partition the curriculum into several courses based on related topics taught in isolation. Students are expected to synthesize their knowledge in a senior design project. It is the authors' experience that students often struggle during their senior design project since they have not gained the appropriate knowledge or mastered necessary skills needed to work on a significant or team-based engineering design project. Specifically, students need to be able to define system requirements, partition the design into subcomponents, design, build, test, and verify that the system requirements have been met. The authors have enhanced and implemented three courses to develop system engineering knowledge and skills that better prepare students for their senior design experience. This paper gives an overview and lists the learning outcomes for each of these courses and includes some examples of laboratory projects that are used to meet these learning outcomes.

#### Introduction

In the current global environment it is imperative that engineering graduates are prepared to enter the workforce with the skills necessary to make immediate contributions. Today, companies often outsource engineering tasks and projects that could otherwise be done by entry-level engineers. Globalization combined with economic pressures has increased the competition for entry level engineering jobs and therefore it is even more important to prepare our engineering graduates with all of the skills needed to be productive members of an engineering team.

The challenges associated with preparing engineering graduates for professional practice through an undergraduate curriculum based on theory and analysis is widely acknowledged. It has become clear that project-based learning with open-ended design projects facilitates self-directed learning and enhances students' project management and communication skills. Typical projects span multiple academic terms, during which time students gain invaluable experience applying and synthesizing material from a variety of courses and disciplines. These projects, as nearly as possible, replicate the working environment that students' will encounter after graduation. The issues encountered while working on projects are different from typical homework assignments in conventional courses. Students gain experience as part of a project team that enhances their ability to bridge into professional practice in an era that requires lifelong learning in the engineering discipline and the ability to perform as a member of a multidisciplinary team. Students gain experience as a member of a multidisciplinary team.

From 2001 to present, our students successfully completed over 25 masters theses and 30 senior projects while conducting research and working on real-world sponsored projects in the *NetPRL* lab. <sup>4</sup> The authors have had the opportunity to work with graduate and undergraduate students from computer engineering, computer science, electrical engineering, software engineering, industrial engineering and manufacturing engineering. The students contribute to research and engineering design projects; at the same time they gain industry-like work experience. Our experience with project-based learning has uncovered several important issues. First, students often have not participated on a large scale team-based design project before and

therefore they have to learn how to work in such an environment. They must gain project management experience, develop a technical specialization to support their project role, and develop their ability to collaborate and contribute to multidisciplinary projects. Secondly, we discovered that our students were not prepared to develop complex systems requiring custom printed circuit boards (PCB). In order to design a complex digital system today, printed circuit board design knowledge and Computer Aided Design (CAD) tool training is usually required. Students typically do not acquire printed circuit board design experience in community colleges or in the upper division courses at Cal Poly, San Luis Obispo. In fact, our experience and research indicate that there are very few universities that offer upper division courses in printed circuit board design or electronics manufacturing.

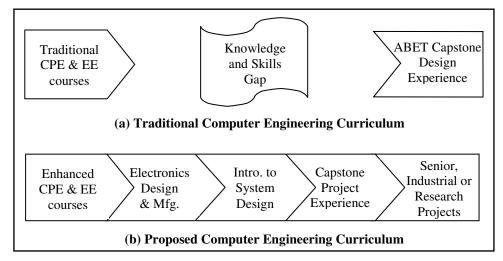

Layering upon the above noted educational deficiencies in engineering curricula, programs generally do not present an integrated approach to engineering education that includes practical application of theoretical knowledge. Students often master the course and laboratory work associated with courses in the curriculum, but they do not gain a "systems" level engineering experience that requires them to synthesize what they have learned in their curriculum and extend their knowledge through independent learning that reaches outside their field of study. The need for "systems" level design and multidisciplinary experiences has been echoed by the Cal Poly computer and electrical engineering Industrial Advisory Board (IAB) and the Accreditation Board for Engineering and Technology<sup>5</sup> (ABET). This educational gap is common amongst engineering curricula. Figure 1 (a) below illustrates the knowledge and skills gap between traditional computer and electrical engineering curricula and those engineering skills required for successful job performance. At Cal Poly, the traditional CPE and EE courses taken before systems design and the capstone project sequence include, computer engineering orientation, fundamentals of computer programming I, II and III, discrete structures, digital design, computer design and assembly language programming, electric circuit analysis I, II and III, continuous-time signals and systems, semiconductor device electronics, and digital electronics and integrated circuits. Several other courses are taken concurrently with the system design and capstone project courses including, systems programming, operating systems, computer networks, computer architecture, along with three technical electives and engineering support courses.

Figure 1. Traditional and Proposed Computer Engineering Curricular Pipeline

The authors have enhanced and implemented three courses to develop system engineering knowledge and skills that better prepare students for their senior design experience. Specifically, the junior-level microcontroller design course, CPE 329, was enhanced to provide a systems design philosophy utilizing modern computer aided design tools. In this course students have the opportunity to design a custom computer system, interface external hardware and develop firmware to best meet system design requirements. A separate technical elective course has been created for students to learn printed circuit board design using CAD tools that build upon the microelectronics, digital and analog design taught in the core courses of the curriculum. Finally, a capstone design course has been created that incorporates team building, engineering design skills, project management, engineering ethics and other related skills.<sup>6</sup> These three courses construct a critical pipeline in the computer engineering curriculum to properly prepare students for the workforce and graduate studies by engaging them in project-based learning activities earlier and developing the appropriate skills needed to contribute to significant team-based development projects. Figure 1(b) illustrates how the core curriculum has been enhanced to fill the knowledge and skills gap with the construction of a pathway to acquire superior student skills through requisite participation in project-based learning projects.

This paper provides an overview and lists the learning outcomes for each of these courses and includes some examples of laboratory projects that are used to meet these learning outcomes. One of the Capstone design projects, the BitNinja I/O extender card, is profiled at the end of this paper. The student project was to design, implement, test, and produce a low-cost I/O extension board to support the systems design course at Cal Poly, San Luis Obispo.

#### **Project-Based Learning Teaching Methodology**

The traditional lecture-based teaching format that currently predominates in engineering education may not be the best way to achieve learning outcomes. There are two major drawbacks associated with this teaching methodology. One is that it fails to develop complete skills and abilities desired in a contemporary college graduate, especially non-technical skills such as communication and project management skills. The other is that problem-solving skills can be developed only through practice, not by watching and listening to a lecture. Shifting the undergraduate culture of receivers into a culture of inquirers, or from passive learning to active learning, is recommended by the Boyer Commission report.

Project-based learning overcomes the two drawbacks discussed above. In the project-based learning approach, students are presented with a challenging project, and the students decide how to solve the problem within a set of constraints. The learning model is shifted from "*Teacher-Centered*" to "*Learner-Centered*" and includes active learning methods. This learning methodology has gained increasing popularity in engineering education recently as evidenced by many recent project-based learning papers published in the educational literatures. <sup>12-14</sup> Project-based learning is consistent with the 2007-2008 ABET accreditation criteria 5 that require engineering programs to demonstrate that their students attain:

3 (c) an ability to design a system, component, or process to meet desired needs within realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability

- 3 (d) an ability to function on multi-disciplinary teams

- 3 (f) an understanding of professional and ethical responsibility

- 3 (g) an ability to communicate effectively

- 3 (i) a recognition of the need for, and an ability to engage in life-long learning

- 3 (k) an ability to use the techniques, skills, and modern engineering tools necessary for engineering practice.

# **Introduction to Systems Design Course**

The exponential increase in the number of transistors available per integrated circuit over the past four decades has fueled the information age and an era of ubiquitous computing. CAD tools allow engineers to work at higher-levels of abstraction to design increasingly more complex systems. Embedded system design has been a keystone course in electrical and computer engineering curricula. Today it is possible for students to design embedded systems using soft-core processors, peripheral devices, and custom hardware on a single Field Programmable Gate Array (FPGA).

In the *Introduction to Systems Design* course at Cal Poly, CPE 329, students themselves design their computing platform using only the necessary hardware and peripheral devices. <sup>15-16</sup> They analyze system performance based on hardware and software tradeoffs against a backdrop of hardware resources utilization metrics, thus vastly increasing the design space they consider for their projects. New content in introductory embedded systems courses using a soft-core approach can be summarized as:

- Increased design space considerations

- Hardware software co-design

- Increased exposure to hardware

- Hierarchical, modular, reconfigurable, and reusable design processes

- Increased cost, performance, and power considerations

- Exposure to the benefits of Programmable Logic Devices (PLDs) and FPGAs: flexibility, board area savings, operating performance, reliability, time to market, power consumption, electromagnetic interference, and design security

- Customized peripheral selection and student-defined memory mapped I/O

- Custom peripheral design

Students do not get the same experience using off-the-shelf microcontrollers since they cannot customize the computer system nor can they design user-specific hardware as part of a system-on-a-chip. A soft-core processor approach expands the design space in which students develop embedded systems incorporating numerous design decisions along the way.

This course is an upper division course for electrical and computer engineering students that have completed course work on electronics design, digital design and computer programming. The class meets three times per week for fifty minutes in a classroom setting and once each week for three hours in the laboratory over the ten weeks of an academic quarter. In the lecture students are introduced to the design, implementation and testing of programmable logic

microprocessor-based systems. Students learn how to interface the embedded system to various sensors and displays. The learning outcomes of this course are that students will be able to:

- determine and document system requirements for a student proposed design project

- select the appropriate design type, hardware or stored program, to meet the system requirements while optimizing various cost functions

- use digital, analog, and serial input and output devices such as UART, SPI, I2C, PS2, LCD, VGA, Keypad, Keyboard, RAM, LED, etc.

- design, implement, and verify a digital system using a hardware description language

- design, implement, and verify a system using a higher-level programming language

- analyze hardware vs. software tradeoffs such as performance, power consumption, system economics, and design time

- document design using block diagrams, flow charts, verification test matrix and system measurements

- select external components and interface to embedded system using product datasheets

- exercise communication skills through preparing a proposal, writing final design reports, and presenting in class.

In the laboratory students get an opportunity to design five embedded systems that meet a specific set of system requirements. They first design a digital clock using the VHDL hardware description language to implement a hardware-based design. Then they use a soft-core processor with a hardware timer and a general purpose input/output peripheral module to design an interrupt driven microcontroller implementation of the same digital clock system. The students are asked to reflect on the design process and analyze the hardware utilization (such as the number of programmable logic blocks and memory space used) and power consumption tradeoffs involved in the two vastly different designs. Other design projects add serial and analog input and output and have more challenging firmware requirements. The students select their own final design project by drafting the system requirements and system architecture in a proposal that is submitted to the instructor for approval. The overall schedule of the lab is shown in Table 1. The laboratory learning modules include:

- introduction to the FPGA development board

- tutorial for Embedded Developers Kit (EDK)

- tutorial for the debugging tools

- hardware datasheets, reference manuals and specifications

- online procedure to submit the design projects for evaluation

Table 1. Overall Schedule of the Laboratory Course

| Week | Laboratory Activities (3 hours/week)                                    |

|------|-------------------------------------------------------------------------|

| 1-2  | Hardware-based digital clock design                                     |

| 3    | Stored-program computer system using LCD display                        |

| 4-5  | Stored program-based digital clock design                               |

| 6-7  | • Function generator (sinusoidal, sawtooth, and pulse width modulation) |

| 8-9  | Student proposed final design project                                   |

| 10   | • Final project demonstrations                                          |

# **Electronics Design and Manufacturing Course**

The \$1.3 trillion electronics industry in the United States and around the world continues to grow at a high rate due to an ever-expanding range of electronic applications. Electronics manufacturing is a multidisciplinary field that involves knowledge from the fields of materials engineering, mechanical engineering, electrical engineering, manufacturing, reliability, and statistical analysis. Thus, it is of critical importance to produce engineering graduates skilled in electronics design and manufacturing.

IME 458 *Microelectronics Design and Manufacturing* is an upper division course for electrical engineering, computer engineering and manufacturing engineering students. The class meets two times per week for eighty minutes each in a lecture setting and once each week for three hours in the laboratory over the ten weeks of an academic quarter. Lectures introduce electronics packaging types and identification, the major manufacturing processes, materials, modern electronics assembly, multilayer printed circuit board fabrication, printed circuit board design, and semiconductor manufacturing. A hands-on laboratory experience is an integral part of this course where students are exposed to state-of-the-art electronic design software (Cadence Allegro©) and the assembly of printed circuit boards using a modern surface mount assembly line. The overall schedule of the lab is shown in Table 2. The learning outcomes of this course and laboratory are that students will be able to:

- identify electronics components including through-hole and surface mount components

- explain microelectronic and electronic interconnect technologies including die attachment, wire bonding, flip chip, and encapsulation techniques

- explain the semiconductor manufacturing process including deposition, lithography, ion implantation, and etching

- describe the fabrication process and identify board materials used in multi-layer printed circuit boards

- layout printed circuit boards for both electrical functionality and manufacturability

- design printed circuit boards using stat-of-the-art electronics design automation software

- assemble printed circuit boards using through hole and surface mount assembly processes

- verify circuit functionality

- identify and correct design flaws

- exercise communication skills by writing a final report and presenting in class

Table 2. Overall Schedule of the Laboratory Course

| Week | Activities (3 hours/week)                                 |  |  |  |  |  |  |

|------|-----------------------------------------------------------|--|--|--|--|--|--|

| 1    | • Introduction to Cadence <i>HDL Concept</i>              |  |  |  |  |  |  |

| 2    | Surface Mount: Stencil printing                           |  |  |  |  |  |  |

| 3-4  | • Surface Mount: Pick and place                           |  |  |  |  |  |  |

| 5    | • Surface Mount: Solder reflow                            |  |  |  |  |  |  |

| 6    | • Introduction to Cadence <i>Alegro</i>                   |  |  |  |  |  |  |

| 7-8  | • Alegro: Design rule constraints and component placement |  |  |  |  |  |  |

| 9    | • Alegro: Routing and generation of manufacturing data    |  |  |  |  |  |  |

| 10   | • Final project demonstrations                            |  |  |  |  |  |  |

# **Computer Engineering Capstone Sequence**

The computer engineering capstone sequence is a two quarter course sequence. CPE 350 and CPE 450 are both one quarter courses with 3 hours per week in a lecture format and 3 hours per week scheduled in the design laboratory. During the six month capstone sequence, teams of 4-6 students participate in the design and implementation of a complex system. All students must be assigned one or more roles and be held accountable for their portion of the project. Team roles may include: Project Manager, System Architect, Hardware Architect, Software Architect, Hardware Designer, Software Designer, System Interface, Development Tools Specialist, Product Verification, Product Reliability and Serviceability (RAS), Procurement, Intellectual Property and Customer Liaison. The project must meet the needs of a real user and be deployable for use by those users. More specifically, during the first quarter students engage with a service project or industry sponsor to elicit and establish project requirements. Regular communication between the customer and students enhances the real world character of the project. In the first phase of the project the students produce a system requirements specification and give a presentation to their sponsor for early feedback. The next phases of the project include the conceptual design and usability study. Again students interact with the project customer to obtain meaningful feedback that can be used in assessing design decisions amongst tradeoffs. The team partitions the system into components and documents the system architecture, component interfaces, communications protocols and data structures needed for the project. Students then organize into functional teams and establish design interdependencies and milestones. After the design review, towards the end of the first quarter, students place purchase orders to acquire prototype hardware and development tools.

At the beginning of the second quarter the functional teams design the subcomponents and write software. At times, design changes must be made and schedule recovery plans established. Simulation environments may be used to facilitate progress before hardware is available or functional. After the subcomponents have been implemented and verified, the team begins the system integration and debugging phase of the project. The teams document their designs throughout the design process and give regular project status presentations to the instructors and sponsors throughout the two academic quarters. At the end of the second quarter the students work on customer documentation which includes Installation and User manuals and design documentation to support future maintenance and engineering changes. The projects are demonstrated at the College of Engineering Senior Design Fair that is open to students, faculty, project sponsors, and the Cal Poly community. Table 3 captures the significant project activities, milestones, and deliverables.

Product design and project management theory is presented in the first quarter of the Capstone sequence. Each team must identify one project manager who is responsible for establishing a project Gantt chart and to report on the team's progress throughout the project. It is important that students can become proficient in the project domain without much assistance from the customer or instructor. Students must engage in independent learning to gain the knowledge necessary to perform their assignments. Inter-project *Knowledge Teams* are formed to create centers of competence where students working in a similar area can interact with students from other projects to share their experiences and expertise. Each student is required to document

their individual research by presenting a mini-lecture to the class and writing a technical paper using the IEEE publication format.

Table 3. Computer Engineering Capstone Project Framework

| Project Phase                   | Deliverable                                                                                                            | Milestone                 |  |  |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|

| 1. System requirements          | Requirements documentation                                                                                             | Requirements review       |  |  |  |  |  |  |

| 2. Conceptual design            | System features and specifications                                                                                     |                           |  |  |  |  |  |  |

| 3. Usability study              | Usability case studies                                                                                                 | Design and feature freeze |  |  |  |  |  |  |

| 4. System architecture & design | System block diagram, critical component selection, interface specifications, protocol definition, and data structures | Design review             |  |  |  |  |  |  |

| 5. Component procurement        | Bill of Materials                                                                                                      | Purchase order submission |  |  |  |  |  |  |

| 6. Subsystem implementation     | Functional subcomponent design                                                                                         |                           |  |  |  |  |  |  |

| 7. System Integration           | Completed prototype system                                                                                             | Eng. "Senior Design Fair" |  |  |  |  |  |  |

| 8. User documentation           | Installation manual, user manual and design documentation                                                              | Customer Project Delivery |  |  |  |  |  |  |

Combination of Hardware and Software: As computer engineering is an interdisciplinary field, each project must include substantive hardware and software development. The project must:

- Contain design problems that require hardware vs. software tradeoff analyses

- Require in-depth knowledge of some computer architecture

- Require substantive testing as proof of a deployable system

- Require/allow for simulation to verify design

- Require hardware and software interfacing and integration

- Use a programming language such as C, Java, or assembly

After successful completion of the Capstone sequence, students will be able to:

- Articulate design specifications and criteria by which they are to be measured

- Design and defend a solution to a real-world problem

- Verify that the design implementation solves a real-world problem and satisfies all of the specified project requirements and constraints

- Evaluate the effectiveness of one's own team and other teams' designs

- Effectively contribute one's own disciplinary knowledge on a team as well as locate and evaluate new information

- Contribute to effective project management (e.g., through the use of Gantt charts)

- Effectively communicate with others in a team, fulfilling one's individual role in the project and in interfacing with customers

- Employ principles of effective communication

- Employ ethical practices in all aspects of the design process

- Reflect on aspects of design and the design process

The computer engineering Capstone sequence taught at Cal Poly has evolved over the last three years. Most of the first year projects were sponsored by on-campus research centers such as the *PolyGait* RFID research center. During the second year of the capstone sequence the majority of the projects were sponsored by off campus companies such as the *Jet Propulsion Laboratory* and

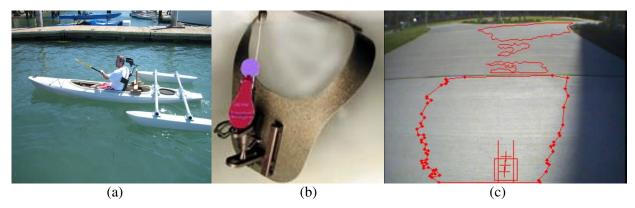

Second Sight Medical. The third year brought a balance between service learning and industry sponsored projects. Examples of the third year projects include: **The Adapted Kayak** for Dr. Kevin Taylor, Kinesiology Department Cal Poly, figure 2-a: **Chin Switch Environmental Remote Control** for VTC Enterprises, Santa Maria, CA figure 2-b: **Personal Obstacle Detection System for People who are Blind** for VTC Enterprises, Santa Maria, CA: **Vision-Based Localization System for Autonomous Vehicles** for Dr. Chris Clark, Computer Engineering Cal Poly figure 2-c: and the **Cal Poly Mars Autonomous Vehicle Project** funded by Lockheed/Martin and Dr. Chris Clark, Computer Engineering Cal Poly.

Figure 2. Computer engineering Capstone Projects

# **BitNinja Team Project Overview**

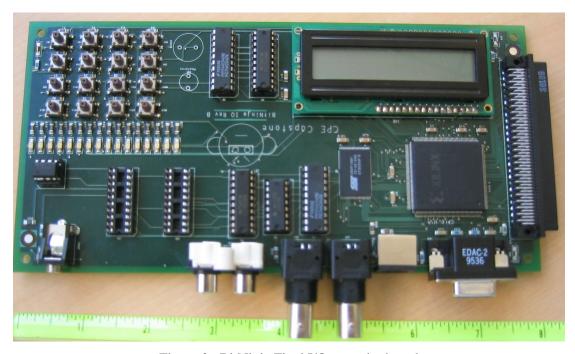

This section of the paper describes a project completed by the Capstone team called BitNinja. The BitNinja team designed an input/output (I/O) extender board that will be used with the Digilent Nexys<sup>22</sup> programmable logic development board currently used in three required computer and electrical engineering digital courses at Cal Poly. All students at Cal Poly are required to purchase this FPGA development board to use in the digital courses. Students must also purchase an assortment of peripheral boards through an online vendor to complete the laboratory design projects in these courses. Unfortunately, there are a limited number of expansion ports on the Nexys development board that can be used for these peripheral boards and purchasing several I/O boards is expensive for the students. The BitNinja project team was tasked with identifying a prioritized list of peripheral input and output devices that are required in the digital courses and designing and implementing a low-cost peripheral board that provides such a set of I/O devices.

The I/O extender board itself contains the input and output devices listed below. The I/O on the board is fully customizable and can be interfaced to a proto-board through a 20-pin header provided on the I/O extender board. This header contains connections to nearly all the I/O connectors, dual operational amplifiers, and power rails.

- 1 Parallel Controlled 16x2 Character LCD

- 1 VGA Connector

- 1 PS2 Connector (keyboard or mouse)

- 2 MB Flash Memory

- 16 Surface Mount Push Buttons

- 16 LEDs

- 1 Speaker

- 2 RCA Connector

- 2 BNC Connector

- 2 Mono Headphone Connector

- 1 Binary Photodiode (Optional, not included)

- Buzzer/Speaker (Optional, not included)

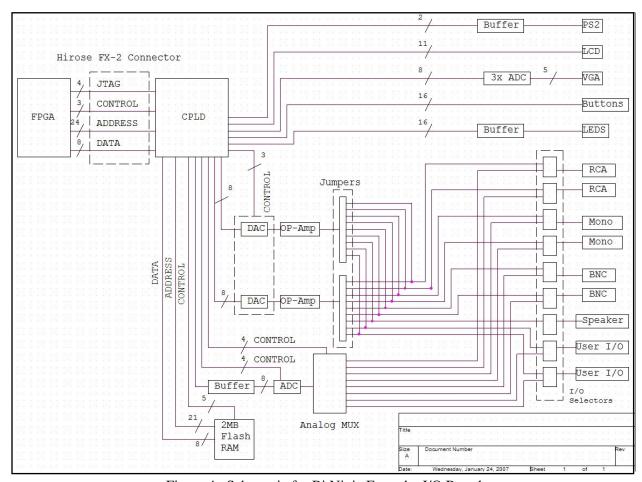

The BitNinja I/O extender board shown in Figure 3 interfaces with the Nexys development board through a 100-pin Hirose FX2 connector. Although the Nexys board provides a 100-pin header, only 40 of these pins are actually available to use for I/O signals and 122 signals are needed to control the I/O devices. The students decided to design an intelligent peripheral board with an onboard controller that could access all of the I/O devices and include programmable logic to support custom hardware state machines used to control external devices such as a VGA controller. A Xilinx XPLA3 complex programmable logic device was selected for the peripheral controller. The schematic shown in Figure 4 was implemented on the 4 by 8 inch 4-layer printed circuit board shown in Figure 3.

The students stated that the IME 458 class prepared them with the necessary skills needed to design a complex multilayer PCB that could be easily manufactured and assembled. The students identified the primary constraint in the design phase was finding robust parts while keeping the end-user cost below \$100. This limited the design choices especially in the analog portion of the board. In particular, the students decided to use a multiplexed analog to digital converter (ADC) system to reduce the number of required ADC components and allow for a wide range of sampling techniques. This decision reduced the component cost considerably while meeting the analog input constraint.

Table 4 includes the Bill of Materials for the prototype I/O extender board. The Xilnx CPLD was donated and therefore the price was not included in the table. It is important to note that these prices were for retail components bought in limited quantities. Significant discounts are available for larger quantity purchases. The BitNinja team received a quote to manufacture the PCB for \$12/board from Advanced Circuits and a quote to assemble the board for \$27/board from KL Electronics. Both quotes were for a quantity of 250 boards. The I/O extender board combined fabrication and assembly cost is approximately \$40/board with a one time setup charge of \$200 and a stencil charge of \$300. Because the I/O extender boards will be sold to the students at-cost, the end user purchase price will be approximately \$100.

Figure 3. BitNinja Final I/O extender board

Figure 4. Schematic for BitNinja Extender I/O Board

Table 4. BitNinja I/O Extender Card Bill of Materials

| Part Description                       | <b>Qnty</b> Unit Price |         | Total   | Supplier | Mfg. Part Number              |  |  |  |  |  |  |

|----------------------------------------|------------------------|---------|---------|----------|-------------------------------|--|--|--|--|--|--|

|                                        |                        |         |         |          |                               |  |  |  |  |  |  |

| Parallel 16*2 character LCD            | 1                      | \$ 8.50 | \$ 8.50 | Mouser   | HDM16216H-B-S00S              |  |  |  |  |  |  |

| High Density D-sub 15p F (VGA)         | 1                      | \$ 0.92 | \$ 0.92 | Mouser   | 587-634-015-263-032           |  |  |  |  |  |  |

| Surface mount green led                | 20                     | \$ 0.16 | \$ 3.20 | Mouser   | SML-LX1206GC-TR               |  |  |  |  |  |  |

| Surface mount pushbutton switch        | 16                     | \$ 0.26 | \$ 4.16 | Mouser   | 101-0664-EV                   |  |  |  |  |  |  |

| Dual PCB mount RCA jack                | 1                      | \$ 0.75 | \$ 0.75 | Mouser   | 161-4218-E                    |  |  |  |  |  |  |

| 3.5mm MONO jack                        | 1                      | \$ 0.77 | \$ 0.77 | Mouser   | 161-3400-EX                   |  |  |  |  |  |  |

| BNC jack                               | 2                      | \$ 2.32 | \$ 4.64 | Mouser   | 5227161-6                     |  |  |  |  |  |  |

| 8-Channel Analog Mux (16 pins)         | 1                      | \$ 0.52 | \$ 0.52 | Mouser   | CD4051BE                      |  |  |  |  |  |  |

| Parallel 8 bit ADC (20 pins)           | 1                      | \$ 4.07 | \$ 4.07 | Mouser   | TLC0820ACDW                   |  |  |  |  |  |  |

| Dual 8 bit DAC (20 pins)               | 1                      | \$ 3.53 | \$ 3.53 | Mouser   | TLC7528IN                     |  |  |  |  |  |  |

| Dual Op-Amp (8 pins)                   | 1                      | \$ 0.55 | \$ 0.55 | Mouser   | LM258P                        |  |  |  |  |  |  |

| 8 x tri-state buffers (20 pins)        | 3                      | \$ 0.50 | \$ 1.50 | Mouser   | MM74HC540N                    |  |  |  |  |  |  |

| Dip 8P socket                          | 1                      | \$ 0.15 | \$ 0.15 | Mouser   | 1-390261-2                    |  |  |  |  |  |  |

| Dip 20P socket                         | 6                      | \$ 0.15 | \$ 0.90 | Mouser   | 2-641612-1                    |  |  |  |  |  |  |

| Dip 16P socket                         | 1                      | \$ 0.15 | \$ 0.15 | Mouser   | 1-390261-4                    |  |  |  |  |  |  |

| 2MB 8bit Flash Memory                  | 1                      | \$ 3.68 | \$ 3.68 | Mouser   | SST39VF1681-70-4C-EKE         |  |  |  |  |  |  |

| Hirose RECEPT R/A 100POS               | 1                      | \$ 7.07 | \$ 7.07 | Digikey  | FX2-100S-1.27DS(71)           |  |  |  |  |  |  |

| 6 Pin Mini-Din Receptacle PS2          | 1                      | \$ 1.16 | \$ 1.16 | Mouser   | 161-2306                      |  |  |  |  |  |  |

| 1206 SMD Capacitor .047uF              | 6                      | \$ 0.20 | \$ 1.20 | Mouser   | 12061C473KAT2A                |  |  |  |  |  |  |

| 1206 SMD Capacitor .010uF              | 6                      | \$ 0.22 | \$ 1.32 | Mouser   | 12065C103JAT2A                |  |  |  |  |  |  |

| 1206 SMD Resistor 1Kohms (SW)          | 18                     | \$ 0.05 | \$ 0.90 | Mouser   | CRCW12061K00JNEA              |  |  |  |  |  |  |

| 1206 SMD Resistor 280ohms (LED)        | 20                     | \$ 0.10 | \$ 2.00 | Mouser   | CRCW1206280RFKTA              |  |  |  |  |  |  |

| 1206 SMD Resistor 390ohms<br>(VGA/PS2) | 5                      | \$ 0.04 | \$ 0.20 | Mouser   | CRCW1206390RJNEB              |  |  |  |  |  |  |

| CoolRunner XPLA3 CPLD                  | 1                      |         |         | Xilinx   | XCR3512XL-10PQG208C<br>(CPLD) |  |  |  |  |  |  |

|                                        |                        |         |         |          |                               |  |  |  |  |  |  |

**Total Component Costs**

\$51.84

In addition to the hardware design, the BitNinja team also designed a default I/O controller for the FPGA using VHDL hardware description language. Students can customize the I/O controller and update the non-volatile CPLD to increase the flexibility of the I/O extender card. In addition, the BitNinja team provided an embedded system reference design that runs a 32-bit Xilinx MicroBlaze soft-core processor in the Nexys development board which communicates to all of the peripheral devices on the I/O extender board. The BitNinja Gantt chart show in Figure 5 indicates some of the work activities and project milestones the team compiled.

|                                   |                      | November |    |    |    | December |    |    |    | January |   |    |    |    | Feburary |        |               |        | March |    |    |

|-----------------------------------|----------------------|----------|----|----|----|----------|----|----|----|---------|---|----|----|----|----------|--------|---------------|--------|-------|----|----|

|                                   | Owner                | 6        | 13 | 20 | 27 | 4        | 11 | 18 | 25 | - 1     | 8 | 15 | 22 | 29 | 5        | 12     | 19            | 26     | 5     | 12 | 19 |

| Solicate Requirements             | Student 1            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Solidify/Communicate Requirements | Student 1            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Define Nexys Interface            | Student 2            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| High-Level Schematic              | Student 2            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        | $\rightarrow$ |        |       |    |    |

| CPLD Hardware Design (VHDL)       | Student 3            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Power Distribution                | Student 1            |          |    |    |    |          |    |    |    |         |   |    |    |    |          | $\neg$ | $\rightarrow$ |        |       |    |    |

| CPLD to Nexys Interface           | Student 2            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| CPLD to Sensor Interface          | Student 4/ Student 5 |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        | $\rightarrow$ |        |       |    |    |

| PCB Layout                        | Student 5            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Tentative Design Completed        |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        | $\rightarrow$ |        |       |    |    |

| CPLD Workbench Testing            | Student 4            |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Design Completed                  |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| First Hardware Rev.               |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| IST                               |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Bug Fixes                         |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Second Hardware Rev.              |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| IST                               |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               | $\neg$ |       |    |    |

| Bug Fixes                         |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        |               |        |       |    |    |

| Completion                        |                      |          |    |    |    |          |    |    |    |         |   |    |    |    |          |        | $\neg$        |        | T.    |    |    |

Figure 5. BitNinja Gantt Chart for Fall and Winter Quarter

#### **Summary and Conclusions**

This paper describes three upper-division courses that have been created or enhanced to include learning objectives and skills that are needed for project-based learning in the computer and electrical engineering curriculum. Students learn how to define system requirements, partition the design into subcomponents, design, build, test, and verify that the system requirements have been met. The project content in each of these courses has been increased to give the students many opportunities to engage in self-directed learning and to get experience as a member of a development team. The students' feedback and final project demonstrations indicate that the courses are providing a solid foundation of systems and PCB design while meeting the learning outcomes of these courses. Students expressed pride in their project accomplishments and gained confidence in their engineering abilities. Through project-based learning, undergraduate students not only learn technical skills to design and manufacture systems, but they also synthesize their engineering knowledge and develop project management, communication and other professional skills.

#### Acknowledgment

This work is based upon work supported by the National Science Foundation, under Grant No. DUE-0633363. The authors want to thank the teaching assistants that helped support the laboratory development for these courses including Jackson Pang, Rafael Kaliski, Don Heyer, and Carter Deleo. We would also like to thank the BitNinja Capstone Team: Joseph Nouri, JJ Krakowski, Will Samuels, Daniel Schacht, and David Herrera and students that provided constructive feedback for this work.

#### **Bibliography**

- 1. Friesen, M. and Taylor, K. L., "Perceptions and Experiences of Industry Co-Operators in Project-Based Design Courses," *International Journal of Engineering Education*, Vol. 23, No. 1, pp, 114-119, 2007.

- 2. Gorman, M. E., Johnson, V. S., Ben-Arieh, D. Bhattacharyya, S., Eberhart, S., Glower, J., et al., "Transforming the Engineering Curriculum: Lessons Learned from a summer at Boeing," *Journal of Engineering Education*, Vol. 90, No. 1, pp, 143-149, 2001.

- 3. Nicolai, L. M., "Viewpoint: an Industry View of Engineering Design Education," *International Journal of Engineering Education*, Vol. 14, No. 1, pp. 7-13, 1998.

- 4. NetPRL webpage at <a href="http://www.netprl.calpoly.edu/">http://www.netprl.calpoly.edu/</a>.

- 5. ABET 2000 *Criteria for Accrediting Engineering Programs*, Accreditation Board for Engineering and Technology, Baltimore, MD, http://www.abet.org/.

- 6. Slivovsky, L. A., "RFID in a Computer Engineering Capstone," Proceedings of the 36<sup>th</sup> ASEE/IEEE Frontiers in Education, pp. 22-27, October 2006.

- 7. Davis, B. G., *Tools for Teaching*, Jossey-Bass Publishers, p.100, 1993.

- 8. Duch, B.J., Groh, S.E., and Allen, D.E., "Chapter 1: Why Problem-based learning? A Case Study of Institutional Change in Undergraduate Education," *The Power of Problem-Based Learning, A Practical "How to" for Teaching Undergraduate Courses in Any Disciplinary*, edited by Duch, B.J., Groh, S.E., and Allen, D.E., Stylus Publishing, LLC, Sterling, Virginia, 2001, pp. 3-12.

- 9. Daems, W., Smedt, B.D., Vanassche, P., Gielen, G., Sansen, W., and Man, H.D., "PeopleMover: An Example of Interdisciplinary Project-Based Education in Electrical Engineering," *IEEE Transactions on Education*, Vol. 46, No. 1, February 2003, pp. 157-167.

- 10. Presley, M. and McCormick, C.B., Cognition, Teaching and Assessment, HarperCollins, New York, 1995.

- 11. Boyer Commission on Educating Undergraduates in the Research University, *Reinventing Undergraduate Education: A Blueprint for America's Research Universities*, State University of New York at Stony Brook for the Carnegie Foundation for the Advancement of Teaching, Stony Brook, NY, 1998.

- 12. Hadim, H.A. and Esche, S.K., "Enhancing the Engineering Curriculum through Project-Based Learning," *Proceedings of the 32<sup>nd</sup> ASEE/IEEE Frontier in Education Conference*, November 6-9, 2002, Boston, MA, Section F3F, pp. 1-6.

- 13. Witt, H.J., Alabart, J.R., Giralt, F., Herrero, J., Medir, M., and Fabregat, A., "Development of Coaching Competencies in Students through a Project-Based Cooperative Learning Approach," *Proceedings of the 32<sup>nd</sup> ASEE/IEEE Frontier in Education Conference*, November 6-9, 2002, Boston, MA, Section F2A, pp. 1-6.

- 14. Ju, W., Oehlberg, L., and Leifer, L., "Project-Based Learning for Experimental Design Research," *Proceedings of International Engineering and Product Design Education Conference*, September 2-3, 2004, Delft, the Netherlands.

- 15. Slivovsky, L. A., and Liddicoat, A. A., "Transforming the microprocessor class: Expanding learning objectives with soft core processors," *37*<sup>th</sup> ASEE Annual Conference, Hawaii, June 2007.

- 16. Slivovsky, L. A., and Liddicoat, A. A., "Work In Progress: Future Pedagogical Trends in the Microprocessor Course The Soft Core Processor," *Proceedings of the 36<sup>th</sup> ASEE/IEEE Frontiers in Education*, pp. 1-2, October 2006.

- 17. Braun, C.G., "Making Things Real in Electronics Laboratories," Proceedings of 1995 FIE Conference.

- 18. Braun, C.G., "An Electronics Prototyping Facility for Undergraduate Electronics Laboratories," *1996 ASEE Annual Conference Proceedings*, pp. 457-465.

- 19. Herniter, M.E., "PC Board Design and Fabrication using Schematics, PADS-PERFORM, and a Laser Printer," *Proceedings of 1994 Frontier in Education Conference*.

- 20. Rizkalla, M.E., O'Loughlin, C., Yokomoto, C., and Burkart, G., "A New Electronic Manufacturing Course for the Electrical Engineering Curriculum," *IEEE Transactions on Education*, Vol. 39, No. 4, November 1996, pp. 512-518.

- 21. Rizkalla, M.E., O'Loughlin, C., and Yokomoto, C., "An innovative model for senior level undergraduate engineering education in electronic manufacturing," *International Journal of Engineering Education*, Vol. 12, No. 2, 1996, pp. 147-151.

- 22. Digilent Nexys Board Reference Manual at http://www.digilentinc.com/Data/Products/NEXYS/Nexys\_rm.pdf